3 卷積碼編碼器仿真

3.1 功能仿真

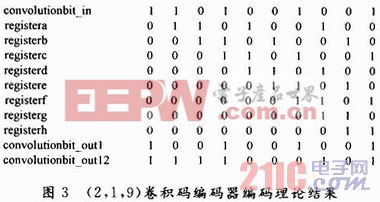

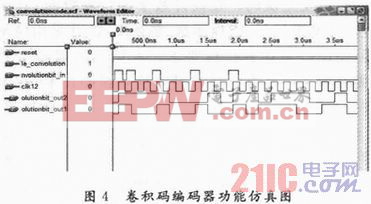

仿真前設置輸入信息序列Convolutionbit-in=“1101001001”�����,對應時鐘為400 ns�。圖3為(2�����,1���,9)卷積碼�,碼發(fā)生器函數(shù)是:g0=(111101011),g1=(101110001)的理論編碼結果����。卷積編碼器VHDL功能仿真波形如圖4所示。本文引用地址:http://www.ljygm.com/article/154639.htm

比較卷積碼編碼器的理論結果(見圖3)和功能仿真圖(見圖4)�,仿真結果與理論計算完全一致。

評論